Robust Watermarking for IC Physical Design IP Production

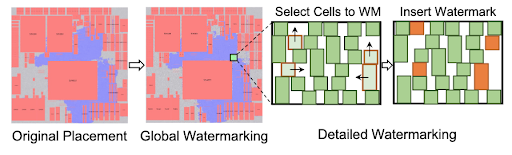

Robust Watermarking for IC Physical Design IP Production Physical design watermarking on contemporary integrated circuit (IC) layout encodes signatures without considering the dense connections and design constraints, which could lead to performance degradation on the watermarked products. We develop ICMarks, a quality-preserving and robust watermarking framework for modern IC physical design. It embeds unique watermark […]